## Chapter 5 Objectives Understand the factors involved in instruction s et architecture design.

- Gain familiarity with memory addressing mode s.

- Understand the concepts of instruction-level pi pelining and its affect upon execution performa nce.

### 5.1 Introduction

This chapter builds upon the ideas in Chapter 4.

CSC3501 - S.J. Park

CSC3501 - S.J. Park

- We present a detailed look at different instructio n formats, operand types, and memory access methods.

- We will see the interrelation between machine o rganization and instruction formats.

- This leads to a deeper understanding of comput er architecture in general.

### 5.2 Instruction Formats

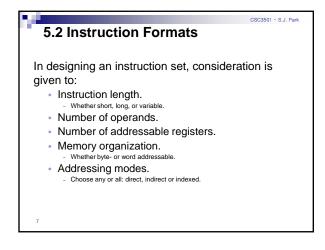

Instruction sets are differentiated by the following:

CSC3501 - S.J. Park

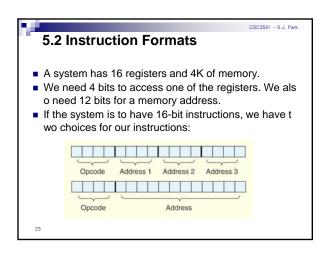

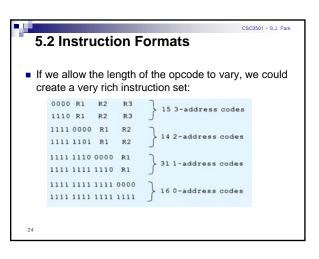

- Number of bits per instruction.

- Stack-based or register-based.

- Number of explicit operands per instruction.

- Operand location.

- · Types of operations.

- Type and size of operands.

### **5.2 Instruction Formats**

Instruction set architectures are measured acc ording to:

- Main memory space occupied by a program.

- Instruction complexity.

- Instruction length (in bits).

- Total number of instructions in the instruction set.

5

### **5.2 Instruction Formats**

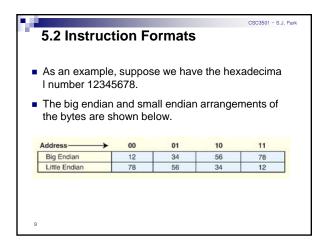

Byte ordering, or *endianness*, is another major arc hitectural consideration.

CSC3501 - S.J. Park

CSC3501 - S.J. Park

- If we have a two-byte integer, the integer may be stored so that the least significant byte is followed by the most significant byte or vice versa.

- □ In *little endian* machines, the least significant byte i s followed by the most significant byte.

- □ *Big endian* machines store the most significant byte first (at the lower address).

### Standard...What Standard?

- Pentium (80x86), VAX are little-endian

- IBM 370, Moterola 680x0 (Mac), and most RISC are big-endi an

CSC3501 - S.J. Park

- Internet is big-endian

- Makes writing Internet programs on PC more awkward!

- WinSock provides htoi and itoh (Host to Internet & Internet to Host) functions to convert

### **5.2 Instruction Formats**

- The next consideration for architecture design con cerns how the CPU will store data.

- We have three choices:

- 1. A stack architecture

- 2. An accumulator architecture

- 3. A general purpose register architecture.

- In choosing one over the other, the tradeoffs are si mplicity (and cost) of hardware design with executi on speed and ease of use.

12

### 5.2 Instruction Formats In a stack architecture, instructions and operands are implicitly taken from the stack. A stack cannot be accessed randomly.

CSC3501 - S.J. Park

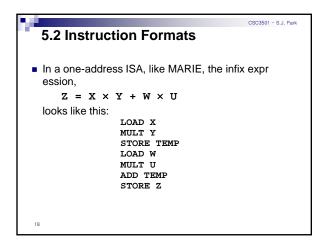

- In an accumulator architecture, one operand of a bin ary operation is implicitly in the accumulator.

One operand is in memory, creating lots of bus traffic.

- In a general purpose register (GPR) architecture, reg

- isters can be used instead of memory.

- Efficient implementation for compilers.

- Results in longer instructions.

- 13

15

### **5.2 Instruction Formats**

Most systems today are GPR systems.

**5.2 Instruction Formats**

14

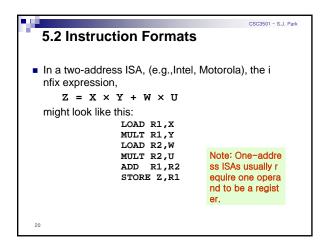

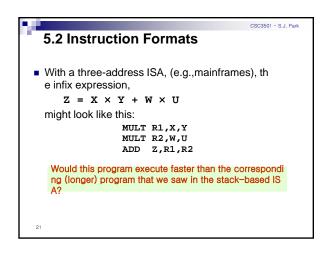

- There are three types:

Memory-memory where two or three operands may

- be in memory.

Register-memory where at least one operand must be in a register.

CSC3501 - S.J. Park

CSC3501 - S.J. Park

- □ Load-store where no operands may be in memory.

- The number of operands and the number of availa ble registers has a direct affect on instruction lengt h.

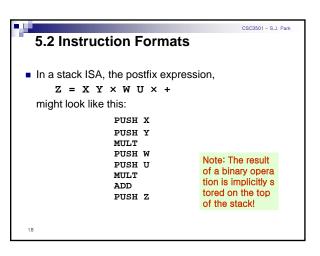

# Stack machines use one - and zero-operand instructions. LOAD and STORE instructions require a single memory address operand. Other instructions use operands from the stack implicitly. PUSH and POP operations involve only the stack's t op element. Binary instructions (e.g., ADD, MULT) use the top tw

o items on the stack.

## 5.2 Instruction Formats The principal advantage of postfix notation is th at parentheses are not used. For example, the infix expression, Z = (X × Y) + (W × U), becomes:

$Z = X Y \times W U \times +$

in postfix notation.